1. Buatlah program menggunakan function untuk menentukan selisih antara dua waktu (jam). Misalkan selisih antara pukul 4.30 dengan 6.00 adalah 90 menit. Terdapat 2 argumen function yaitu jam pertama dan jam kedua (lebih besar dari jam pertama). Petunjuk : buat struktur jam (dengan unit jam, dan menit).

Script program :

#include <iostream.h>

#include <conio.h>

void main()

{

struct data

{

int hour, second;

};

data mula,akhir,selisih;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<" SELISIH ANTARA DUA WAKTU "<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"Jam Mula "<<endl;

cout<<"Jam : ";

cin>>mula.hour;

cout<<"Menit : ";

cin>>mula.second;

cout<<"Jadi : ";

cout<<mula.hour<<"."<<mula.second<<" ";

cout<<endl<<endl;

cout<<"Jam Akhir " <<endl;

cout<<"Jam : ";

cin>>akhir.hour;

cout<<"Menit : ";

cin>>akhir.second;

cout<<"Jadi : ";

cout<<akhir.hour<<"."<<akhir.second<<" ";

cout<<endl;

if((akhir.second-mula.second)<0)

{

selisih.second =(60+akhir.second)-mula.second;

akhir.hour--;

}

else

{

selisih.second=akhir.second-mula.second;

}

selisih.hour=akhir.hour-mula.hour;

cout<<endl;

cout<<"SELISIH DALAM MENIT= "<<(selisih.hour*60+selisih.second)<<endl;

cout<<endl<<endl;

cout<<"Selisih WAKTU : "<<selisih.hour<<","<<selisih.second<<endl;

}

Output Program :

2. Bilangan kompleks memiliki format a+b i, dengan a dan b adalah bilangan real. Notasi a disebut juga bagian real, dan b disebut juga bagian imajiner. Buatlah program menggunakan struktur untuk menjumlahkan, mengurangkan, dan mengalikan 2 buah bilangan kompleks.

Contoh:

(2+3 i) + (-1 + 3i) = 1+6 i

(2+3 i) - (-1 + 6i) = 3 – 3i

(2+3 i) . (-1 + 3i) = -2 – 3i + 6i + 9 i2 = -2 – 3i + 6i – 9 = -11 + 3i

Script program :

#include <iostream.h>

void main ()

{

struct data

{

int bil_re, bil_im;

};

data a1, a2, b1, b2;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<" PROGAM PERHITUNGAN BILANGAN KOMPLEKS "<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"\t I"<<endl<<endl;

cout<<"Masukkan Bilangan Real \t\t=";

cin>>a1.bil_re;

cout<<"Masukkan Bilangan Imajiner \t=";

cin>>b1.bil_im;

cout<<"Jadi :";

cout<<a1.bil_re<<"+"<<b1.bil_im<<"i";

cout<<endl<<endl;

cout<<"\t II"<<endl<<endl;

cout<<"Masukkan Bilangan Real \t\t=";

cin>>a2.bil_re;

cout<<"Masukkan Bilangan Imajiner\t=";

cin>>b2.bil_im;

cout<<"Jadi";

cout<<a2.bil_re<<"+"<<b2.bil_im<<"i";

cout<<endl<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<" Operasi Penjumlahan ="<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"("<<a1.bil_re<<"+"<<b1.bil_im<<"i)"

<<"+"<<"("<<a2.bil_re<<"+"<<b2.bil_im<<"i)="

<<a1.bil_re+a2.bil_re<<"+"<<b1.bil_im + b2.bil_im<<"i"<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<" Operasi Pengurangan ="<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"("<<a1.bil_re<<"+"<<b1.bil_im<<"i)"

<<"-"<<"("<<a2.bil_re<<"+"<<b2.bil_im<<"i)="

<<a1.bil_re - a2.bil_re<<"+"<<b1.bil_im - b2.bil_im<<"i"<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<" Operasi Perkalian ="<<endl;

cout<<"\t\2\2\2\2\2\2\2\2\2\2\2"<<endl;

cout<<"("<<a1.bil_re<<"+"<<b1.bil_im<<"i)"

<<"*"<<"("<<a2.bil_re<<"+"<<b2.bil_im<<"i)="

<<a1.bil_re * a2.bil_re<<"+"<<b1.bil_im * b2.bil_im<<"i"<<"+"

<<a2.bil_re * b1.bil_im<<"i"<<"-"<<b1.bil_im * b2.bil_im

<<"="<<(a1.bil_re * a2.bil_re)-(b1.bil_im * b2.bil_im)<<" +"

<<(a1.bil_re * b2.bil_im)+(a2.bil_re * b1.bil_im)<<"i"<<endl;

}

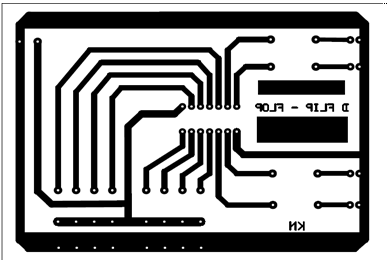

Output Program :

Flowchart :