TRAINER D-LATCH

FLIP-FLOP

LAPORAN

UNTUK MEMENUHI TUGAS AKHIR MATA KULIAH

PRAKTIKUM

ELEKTRONIKA DIGITAL

Yang dibina

oleh Bapak Drs. Suwasono, M.T.

Oleh kelompok 6:

Novita Sari (120534431499)

Wahyu Darmadi Saputra (120534431437)

UNIVERSITAS NEGERI MALANG

FAKULTAS TEKNIK

JURUSAN TEKNIK ELEKTRO

PRODI S1 PENDIDIKAN TEKNIK ELEKTRO

Desember 2013

1. TUJUAN

Ø Mahasiswa dapat menganalisis karakteristik rangkaian D Flip-flop.

Ø Mahasiswa mengetahui prinsip kerja dan karakteristik dari rangkaian D Flip-flop.

Ø Mahasiswa mampu merangkai dan mambuat rangkaian Dflip-flop.

2. ALAT dan BAHAN

Alat

· Solder 1 buah

· Bor PCB 1 buah

· AVO meter 1 buah

· Timah secukupnya

Bahan

· IC 74LS74 1 buah

· Soket IC 14 pin 1 buah

· LED 4 buah

· Resistor 330 Ohm 4 buah

· Resistor 1 K 1 buah

· Kapasitor 47 pF 1 buah

· Switch 1 buah

· Header secukupnya

· Jumper Blackhouse secukupnya

· PCB 1 buah

· Feriklorit secukupnya

3. DASAR TEORI

Flip flop adalah rangkaian yang terdiri dari dua elemen aktif (transistor) yang kerjanya saling bergantian. Flip-flop memiliki fungsi sebagai berikut :

· menyimpan bilangan biner

· mencacah pulsa

· menyerempakkan rangkaian aritmatika

Flip flop bersifat bistable : dua kondisi yang stabil 0 atau 1. Kondisi ini akan tetap stabil tidak akan berubah jika tidak ada input yang masuk.

Flip-flop yang banyak dikenal ada 3 macam, yaitu :

1. Flip-flop Set-Reset (FF-SR)

2. Flip-flop Delay atau Data latch (FF-D)

3. Flip-Flop J-K (FF-JK)

FF-D memiliki 1 input yang disebut D (Data) serta 2 output yang disebut Q dan

Gambar 1.1 Rangkaian dasar Flip-Flop S-R

Tabel pengoperasian Flip-Flop D

Masukan

|

Keluaran

| ||||

Clock

|

D

|

S

|

R

|

Qn

|

Qn’

|

0

|

1

|

1

|

0

|

Hold

|

Hold

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

Hold

|

Hold

|

1

|

0

|

0

|

1

|

0

|

1

|

Sehingga jika disederhanakan, maka tabel kebenaran FF-D adalah :

Tabel kebenaran FF-D

Masukan

|

Keluaran

| |

Clock

|

D

|

Qn+1(QB) = Q

|

1

|

0

|

Hold

|

1

|

1

|

Hold

|

0

|

0

|

0

|

0

|

1

|

1

|

Dimana keluaran FF-D akan sama dengan masukkannya, Jika D = 1, maka Q = 1, jika D = 0, maka Q = 0.

4. PERANCANGAN ALAT

1. Siapkan alat dan bahan yang dibutuhkan

2. Simulasikan rangkaian pada aplikasi livewire atau sejenisnya.

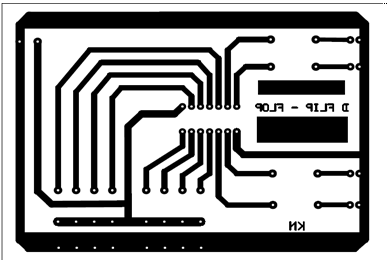

3. Design gambar rangkaian ke dalam bentuk Layout PCB. Export ke PDF melalui menu print.

Gambar Layout PCB

4. Proses penyetrikaan pada papan PCB kosong (sesuaikan ukuran) dengan paper tetap menempel.

5. Rendam PCB ke dalam air hingga kertas papernya terlepas.

6. Larutkan PCB yang telah disablon ke larutan Feriklorit (FeCl3) untuk menghilangkan tembaga pada bagian yang tidak dibutuhkan.

7. Setelah selesai, bersihkan PCB dengan menggunakan tinner dan gosok secara perlahan.

8. Berikutnya proses pengeboran PCB. Lubangi setiap pin pada PCB menggunakan bor.

9. Berikutnya kita dapat memasang komponen pada PCB kemudian komponen kita solder dengan timah sebagai perekat.

10. Potong kaki komponen yang telah di solder jika kakinya terlalu panjang.

11. Pastikan semua komponen terpasang dengan benar sesuai dengan jalurnya.

12. Rangkaian siap di uji coba.

5.

PROSEDUR

KERJA

1.

Siapkan

alat dan bahan yang digunakan.

2.

Susun

rangkaian sesuai gambar. Pada SD = 1 dan CD = 1.

3.

Berikan

input clock dan D sebagaimana Tabel 6.1.

Dimana

untuk clock 1 = saklar dilepas, sedangkan clock 0 = saklar ditekan

4.

Jika

memakai tegangan VCC, hubungkan clock dan D pada function positif jika

berlogika 1 dan negatif jika berlogika 0.

5.

Tulislah

hasil output pada tabel 6.1

6.

Berikan

analisis terhadap hasilnya.

7.

Buatlah

kesimpulan dari praktikum yang telah dilakukan.

6.

DATA

HASIL

Tabel 6.1 Data

hasil Pengamatan Flip-Flop D

D

|

Clock

|

Q

|

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

1

|

7.

ANALISIS

Ø Dari data diatas dapat dilihat keluaran Q berlogika sama dengan

inputan D-nya. Akan tetapi masih ada keluaran yang tidak sama dengan input D,

hal ini dikarenakan data masih dalam keadaan HOLD atau masih merekam data

sebelumnya.

Ø Ketika

Clock pada posisi 0, apabila D berada di posisi 1 maka output Q bernilai 1.

Sebaliknya, apabila D bernilai 0 maka output Q bernilai 0.

8.

KESIMPULAN

·

D

flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer pada reset

inputnya.

·

Sifat

dari D flip-flop adalah bila input D (Data) dan pulsa clock berlogik 1, maka

output Q akan berlogika 1 dan bilamana input D berlogika 0, maka D flip-flop

akan berada pada keadaan reset atau output Q berlogik 0.

·

Pada

saat kondisi clock rendah, sinyal masukkan D tidak mempengaruhi keluaran Q.

Sedangkan untuk sinyal clock yang tinggi,maka akan diperoleh keluaran sesuai

data D yang masuk saat itu.

9.

KRITIK

& SARAN

Dalam percobaan rangkaian Dflip-flop masih sering kita temukan data

keluaran D yang hold atau masih merekam data sebelumnya. Hal ini menghambat

data keluaran Q yang seharusnya sama dengan data inputan dari data D. Jadi,

mahasiswa terlebih dahulu harus mengetahui karakteristik dari rangkaian yaitu D

flip-flop. Maka jika terjadi keluaran yang tidak sesuai, mahasiswa tidak akan

kebingunan untuk mencari keluaran yang benar.

Ø Saat dilakukan pengujian rangkaian ternyata terjadi sedikit

permasalahan yaitu pada salah satu keluaran output/nyala lampu LED pada PCB

susah menyala.

·

Pensolderan

sebaiknya dilakukan dengan benar dan baik.

Ø Keluaran kedua outputan antara Q1 dan Q2 terkadang tidak berjalan

secara bersamaan.

·

Harus

dilakukan pemencetan clock selama 2 kali jadi keluarannya akan sama antara Q1

dan Q2.

nomer hpnya berapa?

BalasHapus